Rapid advances in AI, HPC, and other technologies are increasing demands on semiconductor performance and energy efficiency. Traditional packaging technologies are struggling to meet the needs of the AI era, creating an opportunity for advanced semiconductor packaging technologies to shine.

This has led many major semiconductor companies to invest heavily in this field. Recently, Broadcom announced new advances in advanced packaging technology.

Broadcom introduces first 3.5D F2F packaging technology to meet AI computing demands

Broadcom recently announced its 3.5D eXtreme Dimension System-in-Package (XDSiP) platform on its official website. This is the industry’s first 3.5D F2F packaging technology, integrating over 6000mm² of silicon and up to 12 HBM memory stacks into a single package. This technology meets the high efficiency and low power requirements of AI chips.

Broadcom highlighted the need for 3D stacking to achieve better form factors, power, and cost efficiencies with the advent of new and increasingly complex large-scale language models (LLMs). 3.5D integrated technology, which combines 3D silicon stacking and 2.5D packaging, is poised to become the preferred choice for next-generation XPUs over the next decade.

Broadcom’s F2F technology connects the top metal layer directly, providing a dense, reliable connection with minimal electrical interference and superior mechanical strength.

Broadcom said it worked closely with customers to develop the 3.5D XDSiP platform leveraging TSMC’s technology and tools from its EDA partners. By vertically stacking chip components, this platform allows chip designers to choose the best manufacturing process for each component while reducing interposer and package size, significantly improving performance, efficiency, and cost. You can.

Currently, Broadcom has developed more than five 3.5D products. Most of the company’s consumer AI customers have adopted the 3.5D XDSiP platform, which is expected to begin shipping in volume in February 2026.

Advanced packaging innovation driven by AI boom

The proliferation of AI has facilitated the emergence of advanced packaging technologies, attracting significant investment from many companies. In addition to Broadcom, TSMC, Samsung, ASE, and Intel are also actively developing these technologies.

TSMC: Pioneer of advanced packaging with CoWoS and SoIC

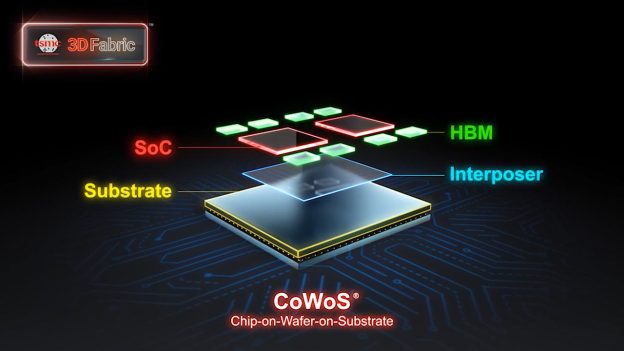

TSMC’s CoWoS advanced packaging technology has attracted great attention in the market. The company is also investing heavily in developing SoIC packaging technology. TSMC has integrated the packaging process into a 3D fabric system that consists of three parts: the SoIC series for 3D stacking technology, the CoWoS series for advanced packaging, and the InFO series.

Introduced in April 2018, SoIC represents a next-generation packaging innovation that combines CoWoS and Wafer-on-Wafer (WoW) stacking technologies. This will enable TSMC to directly manufacture 3D ICs for clients.

The technology will begin small-scale production in 2022, and TSMC plans to expand its production capacity more than 20 times by 2026. Additionally, reports in November revealed that TSMC has secured a 30-hectare area in the Southern Taiwan Science Park to establish an advanced supply chain in a zone focused on advanced packaging, in Chiayi. (AP7) and Tainan (AP8) facilities to support future CoWoS/SoIC production.

Samsung: Develops 3.3D advanced packaging for AI chips

Samsung Electronics announced in July that it is developing 3.3D advanced packaging technology for AI semiconductor chips. Samsung’s concept involves stacking the GPU (AI computing chip) and LCC cache vertically into a single unit and interconnecting it with HBM memory. A silicon bridge chip connects directly to the die, replacing the expensive silicon interposer with a transparent medium for the copper RDL redistribution layer.

This design reduces production costs by 22% without compromising chip performance. Additionally, Samsung plans to incorporate panel-level packaging (PLP) into its 3.3D technology. A large rectangular substrate replaces the limited area of a circular wafer, further improving packaging efficiency.

ASE: Evolving Chiplet Interconnect Technology

In March, ASE announced new chiplet interconnect technology to address diverse chip integration design and advanced packaging needs arising from AI development.

This technology uses microbump technology with novel metal stacking to significantly reduce interconnect spacing between chips and wafers. ASE noted that enhancements in chiplet-level interconnection technology will expand applications in AI chips, mobile application processors, MCU microcontrollers, and other key chips.

Intel: Scaling up 3D Foveros technology

In January, Intel announced that its 3D Foveros advanced packaging technology has entered mass production at its Fab 9 facility in New Mexico, USA. Foveros technology integrates two or more chips with horizontal and vertical interconnects to reduce bump spacing. This approach improves latency and bandwidth by stacking memory on top of active components.

This technology divides the product into small chiplets or tiles, with I/O, SRAM, and power delivery circuitry fabricated on a base die, on top of which high-performance logic chiplets are stacked.

Foveros enables ultra-low-power, high-density chip interconnects, minimizing partitioning overhead and enabling rational selection of chip processes for each block. This improves cost and performance, simplifies SKU creation, and speeds time to market.

(Photo provided by: TSMC)

Previous article

(News) NVIDIA denies rumors of supply suspension in China, promotes local employment of self-driving cars

Next article

(News) It is reported that Samsung will no longer be able to supply HBM3E to NVIDIA in 2024 as the gap with SK Hynix widens.