Thompson, S. et al. 90 nm logic technology featuring 50 nm strained silicon channel transistors, 7-layer Cu interconnects, low-k ILD, and 1 μm2 SRAM cells. In the process. IEEE International Conference on Electronic Devices 61-64 (IEEE, 2002).

Ghani, T. et al. 90nm high-volume logic technology featuring new 45nm gate length strained silicon CMOS transistors. In the process. IEEE International Conference on Electronic Devices 978–980 (IEEE, 2003).

Welser, J., Hoyt, J. & Gibbons, J. NMOS and PMOS transistors fabricated with strained silicon/relaxed silicon germanium structures. In the process. IEEE International Electronic Devices Conference 1000–1002 (IEEE, 1992).

Rim, K., Hoyt, JL & Gibbons, JF Transconductance enhancement in deep submicron strained silicon n-MOSFETs. In the process. IEEE International Electronic Devices Conference 707–710 (IEEE, 1998).

Takagi, SI, Hoyt, JL, Welser, JJ & Gibbons, JF A comparative study of two-dimensional electron phonon-limited mobility in strained and strain-free Si metal oxide semiconductor field effect transistors. J. Appl. Physics. 80, 1567–1577 (1996).

Shinji Ito et al. Effect of mechanical stress on etch-stop nitrides and implications for deep submicron transistor design. In the process. IEEE International Conference on Electronic Devices 247–250 (IEEE, 2000).

Akira Shimizu et al. Local Mechanical Stress Control (LMC): A new technique to improve CMOS performance. In the process. IEEE International Conference on Electronic Devices 433–436 (IEEE, 2001).

Armstrong, M. et al. Forever late: Uniaxially strained silicon transistors in 90 nm CMOS technology. In the process. Symposium on VLSI Technology 50–51 (IEEE, 2004).

Das, S. et al. Transistors based on two-dimensional materials for future integrated circuits. nut. electronic. 4, 786–799 (2021).

Zhu, J. et al. Low thermal budget synthesis of single-layer molybdenum disulfide for silicon back-end-of-line integration on a 200 mm platform. nut. nanotechnology. 18, 456–463 (2023).

Tan, A. et al. Towards low-temperature solid raw material synthesis of single-layer MoS2. ACS application. meter. Interfaces 13, 41866–41874 (2021).

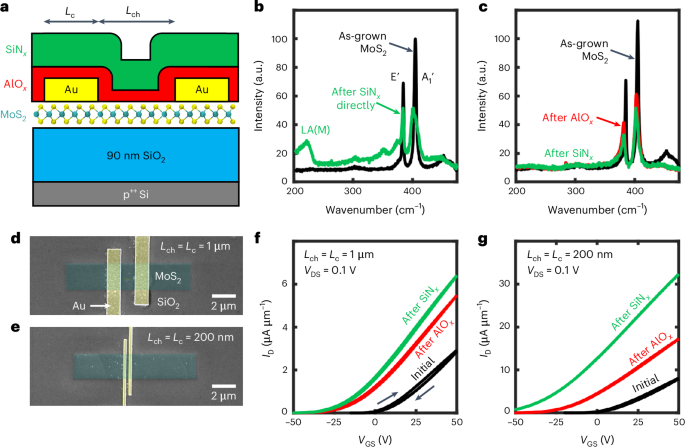

McClellan, CJ, Yalon, E., Smithe, KKH, Suryavanshi, SV & Pop, E. High current density in monolayer MoS2 doped with AlOx. ACS Nano 15, 1587–1596 (2021).

Lan, H.-Y., Oleshko, VP, Davydov, AV, Appenzeller, J. & Chen, Z. Dielectric interface engineering of high-performance single-layer MoS2 transistors via TaOx interfacial layers. IEEE Trans. Electronic Devices 70, 2067–2074 (2023).

Shen, P.-C. et al. Ultra-low contact resistance between semimetal semiconductors and single-layer semiconductors. Nature 593, 211–217 (2021).

Lee, W. et al. Approaching the quantum limit of two-dimensional semiconductor contacts. Nature 613, 274–279 (2023).

English, CD, Shine, G., Dorgan, VE, Saraswat, KC & Pop, E. Improving contacts to MoS2 transistors by ultra-high vacuum metal deposition. Nanolet. 16, 3824–3830 (2016).

Hosseini, M., Elahi, M., Pourfath, M. & Esseni, D. Strain-induced modulation of electron mobility in the single-layer transition metal dichalcogenide MX2 (M = Mo, W; X = S, Se). IEEE Trans. Electronic Devices 62, 3192–3198 (2015).

Hosseini, M., Elahi, M., Pourfath, M. & Esseni, D. Strain-induced mobility modulation in monolayer MoS2. J. Phys. D: Application. Physics. 48, 375104 (2015).

Sohier, T. et al. Electron-phonon interactions in multi-valley materials are enhanced. Physics. Rev. X 9, 031019 (2019).

Google Scholar

Peña, T. et al. Strain Engineering 2D MoS2 with Thin Film Stress Cap Layer. 2D meter. 8, 045001 (2021).

Michail, A., Delikous, N., Parthenios, J., Galiotis, C. & Papagelis, K. Optical detection of strain and doping inhomogeneities in monolayer MoS2. applied physics. Let. 108, 173102 (2016).

Deity, IM et al. Strain-enhanced mobility in single-layer MoS2. Nanolet. 22, 8052–8059 (2022).

Yang, JA et al. Biaxial tensile strain enhances electron mobility in single-layer transition metal dichalcogenides. ACS Nano 18, 18151–18159 (2024).

Chai, Y. et al. Strained gate double layer molybdenum disulfide field effect transistor with edge contacts. Science. Rep. No. 7, 41593 (2017).

Zhang, Y., Zhao, HL, Huang, S., Hossain, MA & van der Zande, AM Enhancement of carrier mobility in single-layer MoS2 transistors by process-induced strain. ACS Nano 18, 12377–12385 (2024).

Kaloyeros, AE, Jové, FA, Goff, J. & Arkles, B. Review – Silicon nitride and silicon nitride-rich thin film technologies: Trends in deposition techniques and related applications. ECS J. Solid State Science. technology. 6, 691–714 (2017).

Mackenzie, KD, Johnson, DJ, Devre, MW, Westerman, RJ & Reelfs, BH Stress control of Si-based PECVD dielectrics. In the process. 207th Electrochemical Society Conference 148–159 (ECS, 2005).

Smithe, KKH, English, CD, Suryavanshi, SV & Pop, E. Intrinsic electrical transport and performance prediction of synthesized single-layer MoS2 devices. 2D meter. 4, 011009 (2017).

Mignuzzi, S. et al. Effect of disorder on Raman scattering of monolayer MoS2. Physics. Rev. B 91, 195411 (2015).

Schauble, K. et al. We reveal the effect of metal contacts on single-layer MoS2. ACS Nano 14, 14798–14808 (2020).

Reboh, S., Morin, P., Hÿtch, MJ, Houdellier, F. & Claverie, A. Mechanics of silicon nitride thin film stressors on transistor-like geometries. APL meter. 1, 042117 (2013).

Hüe, F., Hÿtch, M., Bender, H., Houdellier, F., Claverie, A. Direct mapping of strain in strained silicon transistors by high-resolution electron microscopy. Physics. Pastor Rhett. 100, 156602 (2008).

Thompson, SE et al. 90 nm logic technology featuring strained silicon. IEEE Trans. Electronic Devices 51, 1790–1797 (2004).

Leonhardt, A. et al. Material-selective doping of 2D TMDCs by AlxOy encapsulation. ACS application. meter. Interfaces 11, 42697–42707 (2019).

Thompson, SE, Sun, G., Choi, YS, Nishida, T. Uniaxial process-induced strained silicon: Extending the CMOS roadmap. IEEE Trans. Electronic Devices 53, 1010–1020 (2006).

John, AP, Thenapparambil, A. & Thalakulam, M. Schottky barriers and strain engineering of electrical transport on MoS2. Nanotechnology 31, 275703 (2020).

Manzanares-Negro, Y. Low-resistance electrical contact to several layers of MoS2 by localized pressurization. 2D meter. 10, 021003 (2023).

Chen, Y. et al. A few-layer MoS2 field effect transistor is pressurized in a diamond anvil cell. Nanolet. 17, 194–199 (2017).

Jaikissoon, M., Pop, E. & Saraswat, KC Strain induced by evaporated metal contacts on single-layer MoS2 transistors. IEEE Electronic Devices Letter. 45, 1528–1531 (2024).

Kaushik, N. et al. Schottky barrier height for Au and Pd contacts to MoS2. applied physics. Let. 105, 113505 (2014).

Lim, JS, Thompson, SE & Fossum, JG Comparison of threshold voltage shifts of n-MOSFETs subjected to uniaxial and biaxial tensile stress. IEEE Electronic Devices Letter. 25, 731–733 (2004).

Hashemi, P. et al. High performance and reliable strained SiGe PMOS FinFET enabled by advanced gate stack engineering. In the process. 2017 IEEE International Conference on Electronic Devices (IEDM) 37.3.1-37.3.4 (IEEE, 2017).

Late, DJ, Liu, B., Matte, HSSR, Dravid, VP & Rao, Hysteresis in CNR single-layer MoS2 field-effect transistors. ACS Nano 6, 5635–5641 (2012).

Cheng, Z. et al. How to report and benchmark new field effect transistors. nut. electronic. 5, 416–423 (2022).