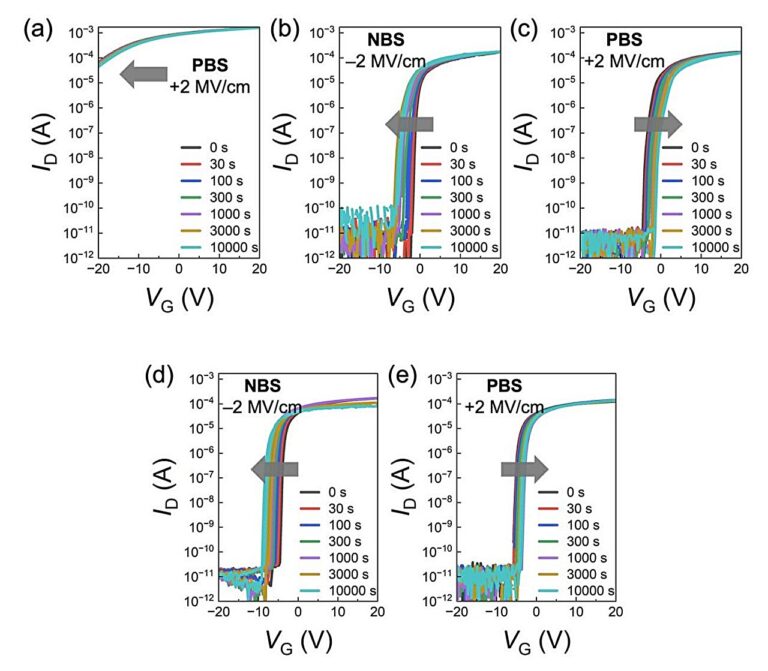

Transfer curves of (a) Al:IZTO, (b) NBS and (c) a single Te heterojunction TFT passivated under PBS at +2 MV/cm for 10,000 s before passivation, (d) NBS and (e) a double Te heterojunction TFT passivated under PBS at VD = 1 V, –2 MV/cm and +2 MV/cm for 10,000 s. Credit: ACS Applied Materials & Interfaces (2024). DOI: 10.1021/acsami.4c02681

A group of Korean researchers recently succeeded in developing a new p-type semiconductor material and thin-film transistor that will lead the innovation in the semiconductor industry. These new discoveries are expected to be widely utilized to improve the overall performance of next-generation displays and ultra-low-power semiconductor devices.

The Electronics and Telecommunications Research Institute (ETRI) has succeeded in developing a p-type Se-Te (selenium-tellurium) alloy transistor that can be easily deposited at room temperature using a simple process using chalcogenide-based p-type semiconductor materials. In addition, they have developed a new technology that can systematically adjust and control the threshold voltage of n-type transistors in a heterojunction structure of an n-type oxide semiconductor and p-type Te by controlling the charge injection of the Te thin film.

The research is published in ACS Applied Materials & Interfaces.

Semiconductors are usually classified as intrinsic or extrinsic depending on their “doping state.” In other words, an intrinsic semiconductor is a “pure” semiconductor with no added impurities. In the case of silicone, a material commonly used in the semiconductor industry, electrons cannot move in pure silicone, so applying a voltage will not result in the same current flow.

Therefore, certain impurities are added to intrinsic semiconductors to take advantage of the semiconductor properties and electrical conductivity of the material. Extrinsic semiconductors are divided into n-type and p-type semiconductors depending on the type of impurity added during the production and manufacturing process.

At present, one of the most widely used materials in the display industry is the n-type oxide semiconductor based on IGZO (Indium Gallium Zinc Oxide). Since p-type semiconductors are inferior to n-type oxide semiconductors in terms of processability and electrical properties, p-type LTPS (Low Temperature Polycrystalline Silicon) is used, but it has many limitations, such as much higher manufacturing costs and limited substrate size.

However, with the increasing demand for higher refresh rates (240Hz+) in high-resolution displays, especially SHV-class resolution displays (8K*4K), interest in the development of p-type semiconductors has peaked in recent years. The demand for p-type semiconductors is rapidly increasing as n-type semiconductor-based transistors used in existing displays have limitations in effectively implementing high refresh rate displays.

To meet these needs, ETRI researchers have succeeded in developing a p-type semiconductor by adding Te to Se, increasing the crystallization temperature of the channel layer, depositing an amorphous thin film at room temperature, and then crystallizing it in a subsequent heat treatment process. As a result, they have succeeded in improving mobility and securing higher on/offline current ratio characteristics compared to existing transistors.

The researchers also confirmed that when a Te-based p-type semiconductor is introduced as a heterojunction structure on an n-type oxide semiconductor thin film, the threshold voltage of the n-type transistor can be adjusted by controlling the flow of electrons in the n-type transistor according to the thickness of the Te. In particular, by adjusting the thickness of the Te in the heterojunction structure, the stability of the n-type transistor is improved without the need for a passivation layer.

Leveraging these achievements is expected to help the next-generation display industry reach new heights of growth, enabling the development of new displays that simultaneously achieve higher resolution and lower power consumption.

In fact, this new discovery will not only make meaningful contributions to the display field, but may also change the landscape of the semiconductor industry. Currently, many of the world’s leading semiconductor manufacturers are focusing on developing new scale-down processes that can increase the integration density of their products, but according to the analysis of many industry insiders, the integration density of semiconductors has reached its limit.

In recent years, new integration methods have been introduced to stack multiple semiconductor chips at once. The best-known of these is the TSV (Through Silicon Via) method, which stacks multiple wafers and drills holes in the wafers to ensure electrical connections. Although the TSV method has the advantages of efficient space utilization and reduced power consumption, it still has many limitations to be resolved, such as high process costs and low yields.

In fact, to overcome these limitations of TSVs, the industry has devised a new approach known as monolithic three-dimensional (M3D) integration, where materials are stacked on a single wafer rather than stacking multiple layers at once. Unfortunately, the M3D approach has yet to reach the commercial stage due to a number of issues, including limited use of high-temperature processes.

However, many experts believe that the heterojunction thin-film transistors and p-type semiconductor devices developed by ETRI can operate stably in processes below 300 degrees Celsius, bringing the industry one step closer to commercializing M3D.

“This is a groundbreaking achievement that can be widely applied not only to next-generation displays such as OLED TVs and XR devices, but also to future researchers in other fields such as CMOS (complementary metal-oxide semiconductor) circuits and DRAM memory,” said Cho Seong-Hyeong, principal researcher in ETRI’s Flexible Electronics Research Division.

ETRI researchers said they plan to optimize the Te-based p-type semiconductors for large substrates of 6 inches or more and apply them in a variety of circuits to ensure their commercial viability, and ultimately find new ways to implement them in new fields.

Further information: Jung Hoon Han et al., “Tuning the threshold voltage of oxide thin-film transistors by controlling electron injection using p-n semiconductor heterojunction structures,” ACS Applied Materials & Interfaces (2024). DOI: 10.1021/acsami.4c02681

Provided by the National Science and Engineering Research Council

Source: Researchers develop new p-type semiconductor material for next-generation displays (September 13, 2024) Retrieved September 13, 2024 from https://techxplore.com/news/2024-09-p-semiconductor-materials-gen-displays.html

This document is subject to copyright. It may not be reproduced without written permission, except for fair dealing for the purposes of personal study or research. The content is provided for informational purposes only.